以原子尺度沉积扩展、超越摩尔定律

-

摘要:

综述 ● 开放获取阅读更多

在过去的几十年中,摩尔定律驱使半导体行业将晶体管的临界尺寸不断缩小至7 nm。随着晶体管进一步缩小到更小的尺寸,该定律达到了极限,芯片上晶体管密度的增加趋势也逐渐放缓。目前,在某些关键步骤中已经使用了极紫外光刻技术,它面临对准精度和大批量生产时的高成本难题。同时,新材料和三维复杂结构的引入给传统自上而下的制造方法带来了严峻的挑战。因此,自下而上的方案被认为是与自上而下制造相结合的必要方法。在本文中,对原子尺度沉积方法进行了回顾和分类,以扩展并超越摩尔定律。首先,沉积可以实现水平方向到垂直分辨率的转变,这一点与自上而下的刻蚀效果相似,例如双重图案化、纳米线的转移、纳米管的沉积等。其次,各种模板辅助的选择性沉积方法(包括介电模板、抑制剂和校正步骤)已用于三维复杂结构的对准。另外,通过固有的选择性沉积可以实现更高的分辨率,并讨论了潜在的选择性机制。最后,还讨论了对高精度和高效率制造的要求,包括设备、集成方法、跨尺度问题等。本文回顾了低维制造和三维复杂结构的集成,以扩展摩尔定律在半导体领域的应用,还有其他新兴领域包括但不限于能源、催化、传感、生物医学等。

命名

ALD原子层沉积

ALE原子层刻蚀

AFM原子力显微镜

CVD化学气相沉积

EPE边缘放置误差

EUV极紫外线

EBID电子束沉积

EBIS电子束雕刻

FET场效应晶体管

FinFET鳍式场效应晶体管

LELE光刻-刻蚀-光刻-刻蚀

MOCVD金属有机化学气相沉积

MOVPE金属有机气相外延

MLD分子层沉积

PVD物理气相沉积

SADP自对准双重图案化

SATP自对准三重图案化

SAQP自对准四重图案化

SAOP自对准八重图案化

STI浅沟槽隔离

SAMs自组装单分子层

STM扫描隧道电子显微镜

STEM扫描透射电子显微镜

VLSI超大规模集成

1.简介

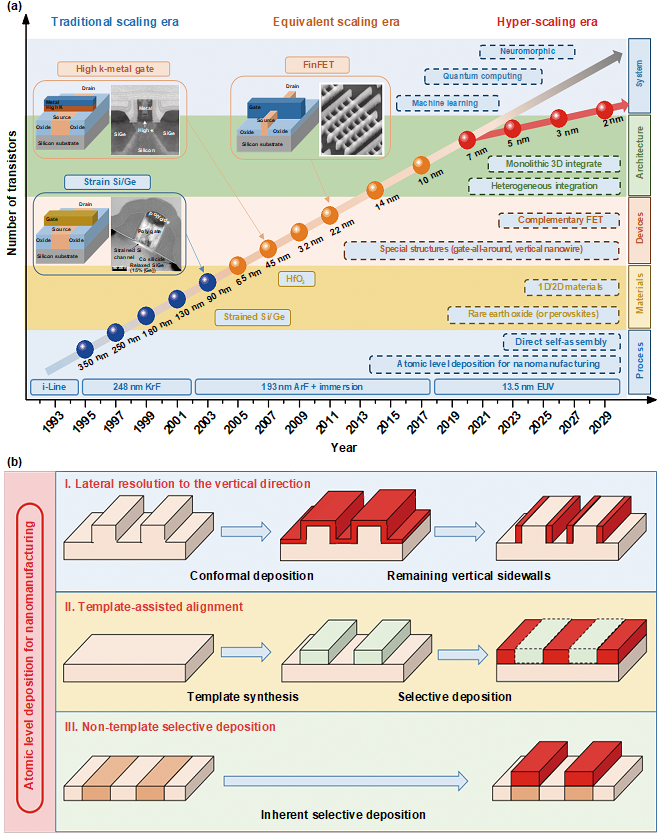

半导体工业的持续发展主要是由减小微电子器件的尺寸驱动的1。值得注意的是,根据1965年的摩尔定律,随着尺寸减小,晶体管的数量每两年每单位面积增加一倍2。此后,该定律预测了直到本世纪初半导体制造业的发展,这在图1(a)中被称为传统的缩放时代。然后,由于光刻的限制,以等比例减小晶体管的尺寸不再可行。在下一个等效的缩放时代,应变Si-Ge 3,4、高-介电金属栅极5和非平面鳍式-场效应晶体管(FinFET)6被成功地应用于超大规模集成(VLSI)电路行业,使得摩尔定律得以延续。非平面FinFET需要更高精度的纳米图案化和对准方法。极紫外(EUV)光刻可以用于某些需要更高分辨率的步骤,但对于批量生产而言仍然非常昂贵7,8。同时,新材料的引入和三维结构的对准非常具有挑战性。在三维纳米结构以及需要高精度和高分辨率的微纳器件或系统中进行图案化十分困难,迫切需要新颖的微纳制造方法。自上而下的减法制造仍然是当前微电子、光学器件和其他应用的微纳制造主流技术。但是,由于考虑了器件的几何形状、密度、性能和成本,非常需要自下而上的增材制造方法9-13。

对于人类来说,将原子作为自下而上的制造基石是一个长久以来的梦想14-17。费曼早在1959年就推测,“底部有足够的空间” 18。该演讲激发了自下而上制造技术的蓬勃发展,包括注塑、3D打印、直接自组装、原子操纵等。注射成型可用于批量生产,但加工精度通常限于微米级19。3D打印可以平衡个性化制造与高通量处理之间的矛盾,但在纳米材料和纳米结构的制造中仍然很难应用20。直接自组装具有原子或分子水平的加工精度,但仅适用于少量的有机材料21。尽管原子操纵可以达到原子级别的控制,但它的方法有限且操作复杂22。因此,自下而上方法的挑战在于同时兼顾效率和精度。

原子和近原子尺度制造已成为制造业的主要发展趋势23,24。在这个大发展时期,研究者开发了各种减法、加法和变革性纳米制造方法。其中,由于厚度可控和区域选择性沉积的特性,研究者对原子级沉积进行了广泛的探索。原子级沉积是一种用于原子或接近原子尺度的纳米材料、纳米结构、纳米器件和纳米系统制造的通用沉积技术。该方法可以减轻制造工艺的复杂度,并且最重要的是能提高分辨率和对准精度。迄今为止,在最先进的芯片制造中采用了许多沉积方法,包括PVD、CVD、ALD等。PVD是一种通过物理方法(例如蒸发、溅射等)将目标材料蒸发到各种基材上的沉积方法,适用于金属、化合物、聚合物等25。CVD是通过基板上前驱物的反应和/或分解而形成薄膜的化学过程26、27。与传统的CVD不同,ALD实现了循环的逐层沉积,该沉积依赖于饱和表面化学吸附和交替前体的自限制性化学反应。因此,ALD显示出可控的膜厚和优异的保形性28-31。通常,沉积速率按PVD、CVD和ALD的顺序降低,而台阶覆盖率则相反32。随着设备的小型化,沉积技术面临着超高精度和大批量制造的挑战。原子级的先进沉积工艺将促进这些问题的解决。

图1.(a)按比例缩放的互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)技术,插图是电子显微镜图像;(b)三种沉积策略分别实现了原子水平的垂直分辨率、模板辅助对准和固有选择性沉积。(插图)经33许可复制。版权所有(2003)爱思唯尔公司。经34许可转载。版权所有(2015)爱思唯尔公司。

本文讨论了原子尺度的沉积技术。通过将原子尺度沉积的材料嵌入到图案化的衬底中,可以实现水平和垂直的埃级分辨率(见图1(b)(I))。例如,双重图案化始于垂直侧壁周围的沉积薄膜层;然后进行各向异性蚀刻以去除硬质掩模,留下薄膜侧壁。它可以提高垂直分辨率,并集成到现有的光刻-刻蚀生产线中35。通过将水平埃分辨率提高到垂直方向,原子尺度沉积还可用于构筑低维结构,例如纳米线、纳米管、纳米孔等。另一方面,晶体管的缩小驱动了半导体和金属的选择性沉积36-38。在图1(b)(II)中,开发了模板辅助的选择性沉积方法来解决对准问题,包括无机模板、带图案的聚合物、自组装单分子层(SAMs)等。选择性沉积存在两个主要挑战:“蘑菇”状生长和非生长区域的缺陷10。为了实现高选择性和对准精度,需要将校正步骤与其他技术集成在一起。为了达到埃级分辨率,讨论了具有高选择性的非模板沉积(见图1(b)(III))。这些方法适用于超尺度结构,包括纳米线、纳米粒子、单个位点等。最后,本文给出了总结和展望。原子尺度沉积对于纳米结构、纳米器件等的制造非常重要,它将扩展摩尔定律,甚至超越摩尔定律。

2.水平方向分辨率转移到垂直方向

原子尺度沉积方法的特征在于薄膜的保形性和均匀性。它可以使水平分辨率转移到垂直方向,获得高深宽比的多样化结构(包括侧壁、纳米线、纳米管等)。特别地,这些方法可以使垂直分辨率减小到亚纳米尺度。垂直方向上分辨率的提高有助于制造更高精度的纳米器件。另一方面,垂直厚度的控制还可以用于改善电子、磁性、声学、光子学等材料性能。原子尺度沉积可以提高纳米图案的精度并获得一些特殊的结构,从而可以进一步减小特征尺寸,增加晶体管的密度,从而在短期内促进摩尔定律的延续。

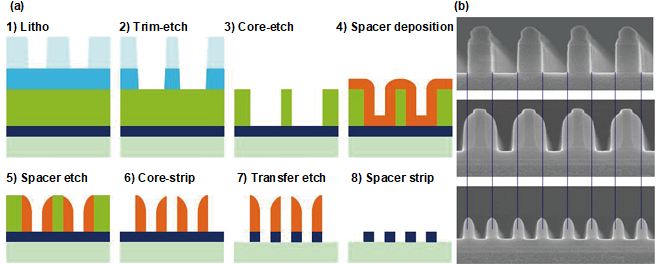

2.1侧壁分辨率

通常,在高深宽比的图案化基板的侧壁上沉积薄膜,可以获得侧壁分辨率。沉积后,可以使用纳米级侧壁膜来提高加工分辨率和器件性能。侧壁分辨率的一个典型案例是双重图案化。解决分辨率限制和控制覆盖形状是VLSI生产的重要制造过程。当前的双重图案化策略主要包括LELE和SADP 39。在LELE中,该过程的特征在于两个连续的曝光步骤,然后将特征尺寸减小到单个光刻的一半。对于SADP,它具有固有的自对准特性和对重叠的强大耐受性。该工艺首先通过等离子体增强的CVD或ALD在垂直的侧壁周围沉积薄膜;然后进行刻蚀去除硬质的掩模版。最后,使得侧壁的半间距减小,如图2所示40。在此过程中,在预图案化的掩模版上获得共形且均匀的薄膜是提高分辨率的关键步骤。获得最终图案的困难在于没有任何残留的去除硬质牺牲掩模版并保持独立侧壁的完整性。双重图案化方法在本世纪初开始使用,它可以进一步提高光刻的分辨率。

晶体管的最小尺寸随着密度的增加而进一步减小,研究者基于重复双重图案化工艺开发了多种图案化方法,这些技术是达到更高分辨率的有效途径。迄今为止,研究者已开发出许多图案化方法,包括SATP,SAQP和SAOP,可以作为芯片制造的有效方案41。Yamato等人42基于上述多图案化方法分别实现了22 nm、11 nm和5.5 nm的半节距。从理论上讲,可以通过重复沉积-刻蚀步骤来进一步提高分辨率。但是,由于工艺耦合的困难和独立式侧壁的力学不稳定性,最终分辨率约为5 nm。该方法利用了垂直方向的精确控制,从而获得了增加的结构密度,这类方法在未来将继续发挥重要作用。

图2. 自对准双重图案化的(a)简图和(b)实例。转载自39,版权所有(2011)Intech Open。

原子级侧壁分辨率可以应用于许多其他区域。例如,侧壁墙已用于隔离FET中的接触/互连金属和介电层43-46。Kumar等人44通过PVD在铜和低K介电层之间沉积了7 nm Ta和3 nm TaN阻隔层,发现Ta隔离墙比TaN层具有更高的台阶覆盖率和更好的均匀性,并且前者具有较低的漏电流和增强的电场强度。如上所述,仅需要超薄层即可显着提高器件性能。

其他的研究是针对光学和磁学的应用进行的。Lavrinenko等人47利用侧壁沉积制备了高深宽比大于20:1的纳米光栅。采用深度反应离子刻蚀的方法制备硅沟道,采用电子束沉积的方法获得6 nm的金层,最后用ALD法均匀生长Al2O3和TiO2。上述应用充分利用了原子尺度沉积在三维结构侧壁上的一致性和均匀性。Buhrman等人48沉积了1.5 nm AlOx作为侧壁屏障,以保护薄膜纳米磁体。该方法首先采用离子束沉积在高Ar分压下均匀地制备Al涂层,然后在氧气气氛中对涂层进行氧化,得到超薄的反铁磁氧化物层。原位氧化层使得该结构具有较高的热稳定性和较低的磁阻尼。

基于侧壁沉积提高垂直分辨率的方法在针对低至1 nm的纳米结构中也获得了应用49-52。Sang等49通过ALD在金属薄膜中创建了垂直取向的纳米间隙,并将结构封装在4英寸晶圆上。间隙宽度的分辨率可低至9.9 Å,可用于具有高通量的电磁纳米器件。以上方法显示出减少诸如光刻和刻蚀之类步骤的优点,并且在侧壁厚度小于10 nm的情况下使得性能得以改善。这些沉积方法在垂直方向上具有精确的厚度控制,可实现一系列应用,包括电子、磁性、光学等。

2.2基于模板的垂直分辨率

在本节中,将针对特殊结构(例如纳米线图案、纳米线间隙、棋盘结构等)中间接利用垂直分辨率的微纳制造方法进行阐述。由于纳米线是低维结构,因此无法通过直接沉积在侧壁上来获得。解决方案通常需要预制模板和其他转印步骤。因此,困难在于获得高分辨率模板并控制转移过程。此外,外场的后处理还可以获得棋盘结构中不能通过直接沉积获得的垂直分辨率。如下,许多研究进行了这类微纳制造方法的探索。

纳米线在微电子学53-56、能源设备57,58、传感器59,60等的应用引起了人们的广泛关注。具有垂直分辨率的纳米线制造通常是通过模板来完成的。如图3(a)所示,Heath等人开发了间距小于13 nm,宽度7 nm的平行纳米线阵列。这个过程称为超晶格纳米线图案转移61,62。首先,通过分子束外延获得具有受控间距的叠层超晶格模板(GaAs / AlGaAs)。然后,选择性地蚀刻AlGaAs层以形成梳状结构。蚀刻后,所需的金属纳米线通过电子束蒸发仅沉积在凸起的GaAs层上。最后,将金属纳米线转移到硅衬底上。该方法与经典的电子产品制造方法兼容,并展示了在一维电子产品中的应用。除了超晶格,其他叠层结构,例如嵌段共聚物63和叠层膜64,都可以用作制备纳米线的模板。通过叠层结构制备纳米线的研究相对较少,值得进一步探讨。

另一个示例是线上光刻。Mirkin等人65,66报告了一种线上光刻方法,该方法在单个纳米线上具有可控的面对面间隙,如图3(b)所示。将分段的Au-Ag和Au-Ni纳米线电化学沉积在受控的多孔氧化铝掩模版中。纳米线的每个部分都可以通过在电化学沉积过程中的电荷量来控制。通过等离子体增强CVD沉积桥接衬底。最终,释放纳米线,并选择性地蚀刻间隙尺寸低至2 nm的Ni。这样获得的具有可控间隙尺寸的纳米线可用于电子和生物传感。与传统的纳米光刻技术(例如电子束光刻、离子束光刻、浸笔式光刻等)相比,该工艺是一种高通量的微纳制造方法。

图3.(a)纳米线图案转移61和(b)线上光刻66。(左)经61许可转载。版权所有(2008)美国化学会。(右)经66许可转载。版权所有(2008)美国化学会。

针对垂直分辨率的棋盘结构也称为垂直排列的纳米复合薄膜,它可以通过温度调节间接实现垂直厚度控制67-69。Driscoll等人69通过脉冲激光沉积在高温下得到了两种混合相。在低温退火之后,将两种混合相分解以形成垂直厚度小于10 nm的纳米棋盘结构。这种结构是通过两相的热力学稳定性和最小界面能之间的差异实现的。有趣的是,这些结构不受基板夹持,并且可以通过具有不同弹性模量的两相之间的晶格失配来实现垂直方向的应变操作。在钙钛矿-尖晶石、钙钛矿-岩盐和钙钛矿-萤石系统中都发现了棋盘结构,这类结构适用于铁电或铁磁设备的应用70。但是,薄膜分解过程受许多重要因素影响,包括膜组成、基底结晶度和生长条件,需要仔细选择材料和调节微结构。棋盘结构很难用传统的沉积方法制备,它为增强功能的垂直分辨率开辟了新的途径。

2.3管壁分辨率

在本节中,将讨论垂直分辨率以外的纳米管和纳米孔。通过自上而下的方法制备纳米管非常困难,因为它是具有纳米级均匀厚度的等效超高深宽比结构。通过沉积对纳米管和纳米孔的精确尺寸控制是垂直分辨率的典型示例,可以用作光电器件、FET、能量存储器件、催化等71-74。

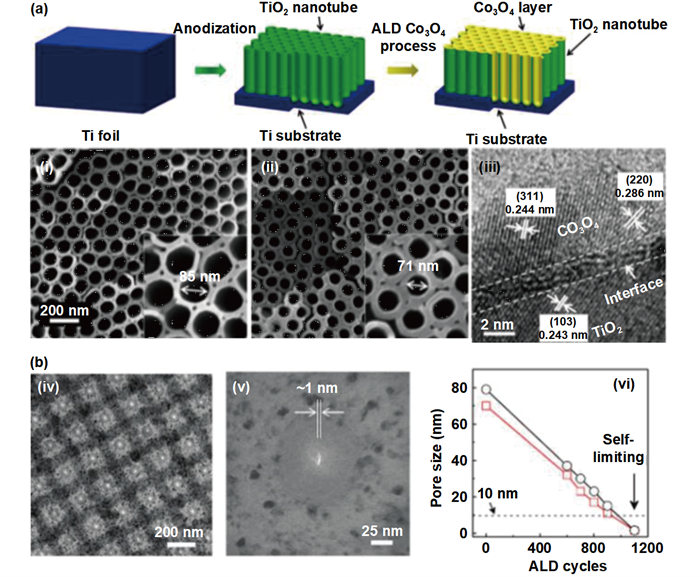

纳米管的形状可以在原子尺度沉积过程中通过垂直膜厚控制进行调整。例如,我们75在可见光光电化学器件中,通过ALD制备了深宽比大于100:1的Co3O4 / TiO2纳米管阵列,如图4(a)所示。通过调整ALD循环次数,可将厚度从亚纳米到10 nm以上的Co3O4层涂覆到TiO2纳米管的内壁上。Co3O4的生长速率约为0.4 nm /周期,通过Co3O4循环数可以控制纳米孔的直径,从而对光电性能进行调控。

当循环数增加时,上述方法可以使纳米孔收缩,直到它们被完全填充。Rossnagel等人76在Si3N4 / TiN / Si3N4膜上制备了ALD修饰的纳米孔,如图4(b)所示。最初的纳米孔是通过电子束光刻制造的。经过1000次TiO2沉积后,孔径从70〜80 nm缩小至仅1 nm。该结构可以用于离子FET。同样,Sainiemi等人77展示了通过控制ALD循环数来调整硅膜上的穿孔。这种类型的硅直通技术已经引起工业界的广泛关注78。该方法的特征在于在预制孔状结构上的保形沉积,可以直接制备难以通过自上而下的方法得到的精细结构。

图4.(a)基于管壁沉积的光电化学器件75和(b)离子FET 76。(上)经75许可转载。版权所有(2015)美国化学会。(下)经76许可转载。版权所有(2009)美国化学会。

除了垂直分辨率,还可以通过收缩纳米孔并随后去除牺牲模板来制造独立式纳米管阵列。纳米管与多孔牺牲模板具有相同的直径,纳米管的厚度可以通过优化模板上的沉积工艺来调整。Sander等人79通过ALD在多孔氧化铝模板上制备了TiO2纳米管,然后通过蚀刻氧化铝掩模释放纳米管。在这种情况下,内径是固定的,并且管壁厚度可以精确地控制在3 nm以下。同样,Ikkala等人80将聚合物纳米棒作为内部牺牲模板来获得纳米管。在ALD工艺之后,聚合物纳米棒在300℃下分解。然后,外部纳米管的壁厚可控制到10nm以下。纳米管具有高的比表面积,可以通过调节尺寸来控制其性能。可定制的纳米管有望在未来的纳米工程中使用。

除了陶瓷材料,碳材料也可以集成到上述制造方法中。Choi等人81通过CVD沉积了垂直排列的碳纳米管,并用于FET领域。阳极氧化铝用作牺牲的模板。通过这种方法制造的纳米管具有20 nm和50 nm的直径。通常,该方法需要预制易于移除的模板而不损害纳米管的完整性。这些沉积方法的垂直厚度可控制在10 nm以下,可以用在FET、传感、光伏和光催化等领域。垂直分辨率以外的其他低维结构将在第4节中介绍。

3.水平方向分辨率转移到垂直方向

随着器件变得越来越复杂,薄膜的对准生长被认为是纳米制造过程中的重要一环。如果不能实现对准,则边缘放置误差(EPE)的问题将非常严重,器件的绝缘性能也将恶化,成品率和稳定性将降低。为了实现高精度对准,要避免或消除不希望出现的成核是一个挑战。当前有两种实现对准的方法:自对准选择性沉积和常规图案化(包括膜沉积、光刻和蚀刻等一系列步骤)10。选择性沉积是一种实现对准的有效且有前途的方法,它可以减少诸如光刻和刻蚀之类的步骤。另一方面,对准是选择性沉积在微纳制造领域中的重要应用。选择性沉积的特征在于仅在指定区域沉积,通常需要模板辅助。模板的目的是限制生长方向和/或阻挡某些区域。沉积发生在模板未覆盖的生长区域,而沉积在覆盖模板的非生长区域受到抑制。对基板差异不敏感的材料,通过某些模板就可以获得或提高选择性。选择性沉积是实现三维堆叠结构对齐的有效解决方案,可以简化微电子制造的下游处理步骤。但是,必须注意的是选择性会丧失,例如“蘑菇”生长,非生长区域的缺陷等10。因此,需要选择性去除,特别是选择性刻蚀,以提高对准精度和边缘取向。

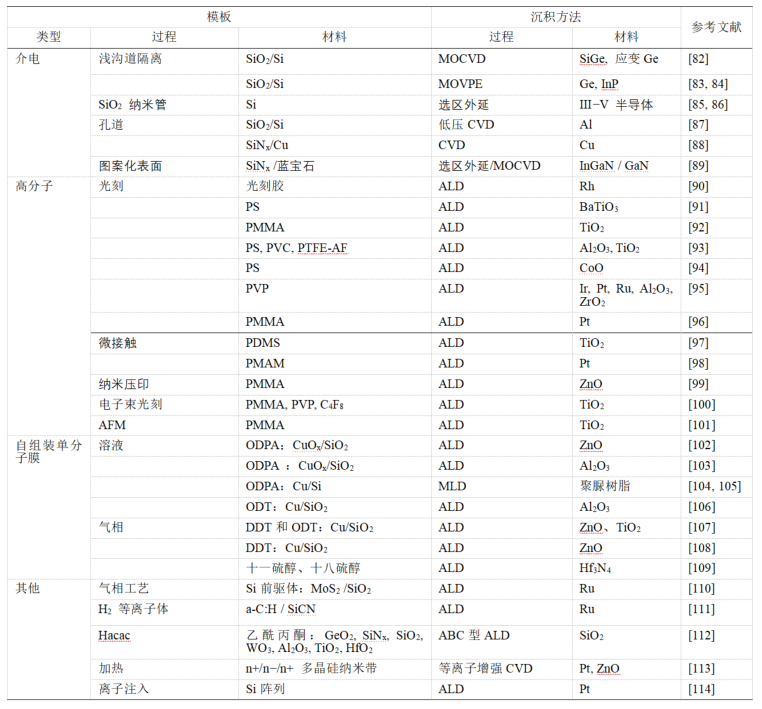

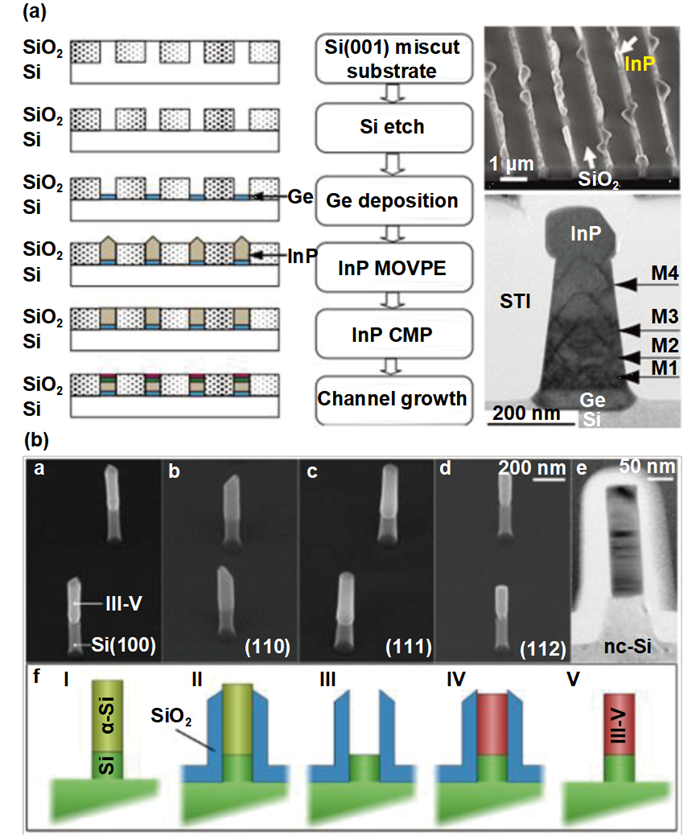

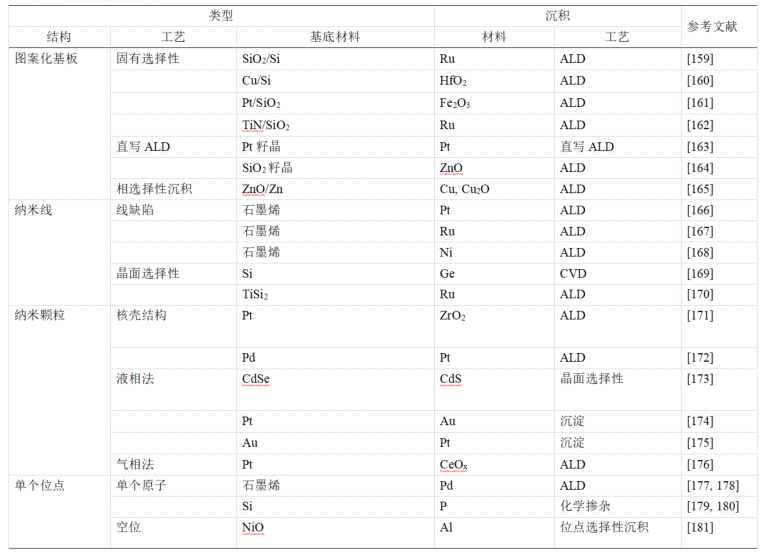

通常,使用特殊的模板可以有效地获得高的选择性。表1总结了不同类型的模板辅助选择性沉积工艺,包括介电模板、图案化聚合物、自组装膜等。值得注意的是,表1中的沉积技术是CVD和ALD。目前,半导体工业中使用的主要沉积技术是CVD。在模板的帮助下,可以快速实现选择性CVD,薄膜厚度可以达到100 nm以上。MOCVD又称MOVPE,是CVD的一个分支。它使用III-V族的有机化合物和II-VI族的氢化物作为晶体生长的来源82-84,采用热分解法在衬底上进行气相外延生长化合物半导体及其固溶体单晶薄膜。由于自限反应的特点,ALD前驱体对基底的表面物种非常敏感,它通常适用于制备10 nm以内的超细结构。ALD甚至可以在没有模板的情况下实现高选择性(如第4节所示)。另外,PVD的选择性报道较少,因为很难抑制高动能的气态粒子在非生长区域的成核。

如何选择合适的模板取决于材料、制造精度、技术成熟度等。介质模板由于其机械刚度大,主要在半导体工业中用于实现选择性沉积。典型的例子是浅沟道隔离(STI)、通孔、孔洞等。通过物理隔离,FET的沟道半导体材料以及接触/互连金属通过MOCVD或MOVPE选择性地生长在所需的表面上。对于一些难刻蚀的材料,需要用光刻技术刻蚀出聚合物模板。沉积后,采取剥离步骤去除聚合物。在某些情况下,沉积发生在聚合物的侧壁和顶面上,这使得剥离步骤具有挑战性。表面自组装膜(SAMs)由于具有区域选择性组装的特点而被广泛应用于表面改性,被认为是解决上述问题的可行方案。前驱体在自组装膜和干净衬底上的吸附速率和反应速率通常存在较大差异,可以实现靶向薄膜的选择性沉积。然而,自组装膜在浸渍或印刷过程中的非常耗时,且不适用于等离子体和高温沉积工艺。为了实现大规模生产,基于气相的改进工艺被大量研究。在未来,区域选择性沉积将显示出广阔的应用前景。借助这些模板,芯片制造商不仅可以直接在三维空间叠加晶体管,还可以集成传感、储能等多种功能,获得超级芯片。

表1. 模板辅助的选择性沉积。(PS:聚苯乙烯;PMMA:聚甲基丙烯酸甲酯;PVC:聚氯乙烯;PTFE-AF:聚二氟-双(三氟甲基)-二恶唑-共-四氟乙烯;PVA:聚(乙烯基吡咯烷酮);PDMS:聚(二甲基硅氧烷);PMAM:聚甲基丙烯酰胺;ODPA:十八烷基膦酸;ODT:十六烷基硫醇;DDT:十二烷硫醇)

3.1基于介电模板的对准

为了实现对准,基于电介质模板的各种结构,例如浅沟槽、通孔、孔道、纳米管等被广泛研究。介电模板具有很高的机械刚度和热稳定性,表现出优异的边缘取向和对准精度。与保形沉积不同,此方法有利于整个目标空间的填充。通常,这些模板的准备需要各种复杂的光刻技术。因此,对齐的精度受到模板形状的限制。当填充物超过模板的高度时,选择性沉积的约束被解除。然后,选择性丧失,并出现“蘑菇”状生长的现象,需要进行额外的后处理,例如刻蚀或抛光。这种策略可以实现快速的空间选择性填充,而选择性沉积的膜厚通常取决于模板的形状。

STI的选择性外延是对准的一个典型案例,它广泛用于集成电路(IC)的大批量生产中82-84、115-122。在IC制造过程中,STI是在沉积高迁移率的材料之前构建的。如图5(a)所示,STI氧化物起着阻断的作用,而Ge / LnP物种仅在沟道区域内才呈现外延生长。该方法可以处理热预算,解决LnP层与衬底之间的晶格失配84。通过MOVPE将LnP层定向沉积在沟槽的顶部,再对“蘑菇”状凸起进行抛光和选择性刻蚀,使得沟道材料在浅沟槽上不断生长。选择性外延生长的通道质量取决于许多不同的因素,例如STI结构、生长条件和后处理过程。例如,Wang及其同事123发现,50 nm宽的沟道具有比20 nm更好的沟道填充能力。Vandervorst等人83研究了三种不同的LnP沉积温度:分别为500℃、550℃和625℃。在低温(500℃)下生长的LnP具有较高的缺陷密度,而在高沉积温度(625℃)下会出现不均匀性、空洞和凹坑。通过在一个基板上集成不同的材料,上述方法可以实现多功能性。

图5.(a)STI模板84和(b)SiO2纳米管阵列的外延生长86。(上)经84许可转载。版权所有(2010)电化学学会。(下)经86许可转载。版权所有(2014)美国化学会。

除了在FET中选择性沉积沟道半导体外,IC的接触/互连金属还可以利用选择性沉积实现侧壁隔离87,88,126-130。例如,Zheng等127通过CVD在小孔的底部选择性地填充了Co。随着通孔的临界尺寸减小到10nm以下,常规铜通孔的归一化电阻大大增加。用Co预填充通孔后,在7 nm节点处电阻降低了30%。填充金属的电导率和选择性在很大程度上取决于孔的形状和沉积过程。介电隔离技术对提高选择性和对准性能具有重要意义。在超级通孔的帮助下,区域选择性沉积将解决半导体工业中规模化制造的工艺难题。对于复杂的结构,可以通过探索适当形状的介电模板来实现对准制造。

3.2基于抑制剂的对准

通过有机基团进行表面修饰是一种广泛研究的对准方法,包括聚合物、SAMs和其他抑制剂分子131。改性后,表面的化学性质将发生变化,从而实现选择性沉积。与介电模板相比,抑制剂更容易去除,但是边缘取向需要改进。

近年来,研究者对图案化聚合物进行了深入研究132,133。例如,光致抗蚀剂被广泛用作区域选择性沉积的掩模层。基于光致抗蚀剂的选择性沉积已应用于芯片的制造。首先,需要通过光刻法暴露出生长区域,实现对聚合物的图案化处理。沉积后,需要进行后剥离或蚀刻步骤以获取目标图案。Krishnamoorthy等人99通过旋涂和纳米压印光刻技术,在Si衬底上制备了纳米多孔PMMA模板。去除PMMA膜后,得到了特征尺寸低至100 nm以下的ZnO纳米阵列。迄今为止,已经研究了许多光刻策略来实现图案化的聚合物模板。Sung等人97通过微接触压印制备了图案化的PDMS薄膜,然后将TiO2薄膜沉积在Si基板上,如图6(a)所示。这些将光刻与选择性沉积相结合的方法将继续在微纳制造中发挥重要作用。

然而,避免在聚合物模板上不希望的成核十分具有挑战性。因此,研究人员开发了用于高分辨率选择性沉积的替代方法。SAMs在文献中被广泛报道,主要用于选择性吸附和表面钝化102,134-138。此外,与聚合物薄膜相比,SAMs可以通过加热轻松去除。通常,SAMs是有机超薄膜,由湿化学方法合成的紧密堆积的单体组成。通常,单体包含三个部分:头基、碳链和尾基。头基通过共价键或离子键化学吸附在底物上。碳链在范德华力的作用下相互排斥,导致排列有序。尾基的特征在于使表面失活,降低表面能。SAMs通常在沉积前浸入溶液中使基材表面失活。

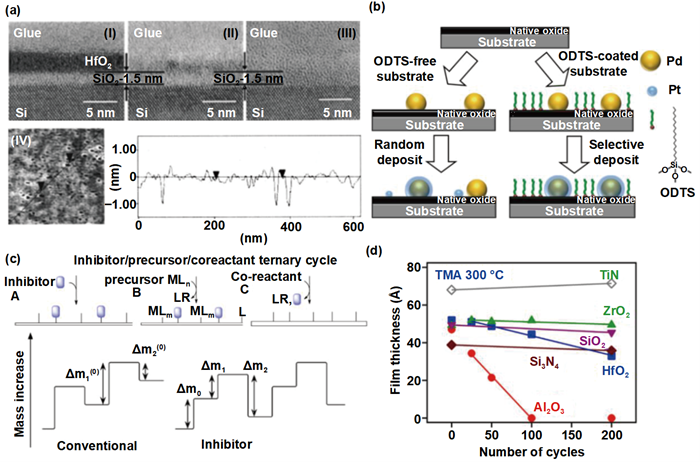

通过液体方法将ODTS选择性地附着在SiO2表面,Bent等人139将HfO2选择性地沉积在Si表面而不是SiO2上,如图6(b)所示。将ODTS更改为1-十八碳烯时,氢端的Si表面被封闭,在ALD过程中Pt成核仅发生在SiO2区域。这种表面钝化策略可以用于许多图案化的金属/介电纳米结构中。据报道,Cu区域被SiO2区域选择性地通过不同类型的SAMs阻挡,然后仅在SiO2区域发生沉积104,106,108,140。其他纳米结构也可以通过SAMs的选择性吸附制备141。Liu等142在Pt纳米颗粒上选择性生长ODT,然后用Co3O4覆盖Al2O3基底。通过煅烧除去SAMs后,就制成了纳米陷阱结构(见图6(c))。通过选择性自组装和选择性沉积,两步选择性极大地扩展了选择性沉积的材料边界,可应用于各种纳米结构的制造。

与聚合物类似,SAMs也可以与光刻技术结合,在同一材料的表面上进行图案化,包括EUV技术136、电子束直写143、浸笔光刻144和纳米压印技术99。通过光刻,可以将生长区域暴露于化学吸附物种中,而非生长区域仍被SAMs阻挡。尽管它面临着较长的处理时间和复杂的工艺耦合的挑战,但能够实现小于100 nm薄膜的区域选择性生长,这在电子应用领域具有诱人的前景。

除SAMs外,基于气相的改进方法也可以实现区域失活。例如,Lee等人110报道,Si前驱物可以用作抑制剂,以实现在SiO2上替代Si的选择性沉积。这种基于气相的工艺可以集成到生产线中,以进行大批量生产。Bent等114通过离子注入选择性地钝化了图案化硅衬底的水平区域,使得Pt仅沉积在垂直区域。这种ALD也被称为地形选择性ALD,如图6(d)所示。这种抑制剂体系相对较少,需要大量挖掘才能满足未来的纳米制造趋势。

图6.(a)聚合物的选择性沉积97;(b)基于SAMs的正胶和负胶图案化139;(c)基于SAMs的纳米阱结构142;(d)通过离子注入的地形选择性沉积114。(a)经97许可转载。版权所有(2006)美国化学会。(b)经139许可转载。版权所有(2006)威利- VCH出版社。(c)经142许可转载。版权所有(2017)威利- VCH出版社。(d)经114许可转载。版权所有(2016)美国化学会。

3.3用于对准沉积的校正步骤

用于选择性沉积的抑制剂分子面临着是否能够阻碍非生长区域的挑战145-149。例如,SAMs的质量受沉积过程中温度和基板条件的影响。因此,在ALD循环中,SAMs的缺陷是不可避免的。低缺陷水平和相应的计量方法对于大批量生产是必需的。在本节中,将讨论带有校正步骤的先进沉积工艺,以提高选择性和对准精度。

选择性由于针孔而降低,如图7(a)所示147。Martinson等149在ALD循环过程中使用了SAMs的非饱和模型来分析成核起始和岛状生长。在第一阶段,SAMs提供了良好的阻止效果。在孕育期,沉积材料的数量没有增加。然后,随着缺陷位置的增加,沉积材料的数量在每个随后的循环中呈指数增长。最终,当成核岛汇合且侧壁面积减小时,发生了线性增长。SAMs的缺陷问题亟需解决,并且随着纳米器件的进一步规模化,相应的纳米级特征结构将变得越来越重要。另外,SAMs的针孔也可以反向利用来生长核壳结构纳米粒子,并且针孔密度可以通过浸入时间来调节150,151。例如,我们150将Pd纳米颗粒沉积在SAMs的针孔上。然后,Pt的沉积仅发生在密集阻塞的SAMs区域中的Pd颗粒上(见图7(b))。SAMs是常用的抑制剂,其性质和应用值得进一步研究。

由于上述问题,结合校正步骤的先进选择性沉积工艺被开发出来。Parsons等人152发现,在图案化的SiO2 / Si衬底上,W的选择性沉积仅在几个循环后就会降低。通过将H2添加到W前驱体中,SiO2区域生长至少会多延迟10个循环。研究人员将钝化效应归因于HF的形成,HF钝化了SiO2区域或去除了表面物种。这种稀释的WF6输运方法扩展了纳米器件的选择性窗口。据报道,氢和氢等离子体是抑制材料沉积在碳基图案上的有效方法111,153,154。这些方法已被证明可以减少非生长区域的杂质和不希望的边缘取向。

除了校正的AB型策略外,研究者还开发了先进的ABC型沉积方法。通过在一定数量的AB型ALD循环后重复表面改性步骤,可以实现超高的纳米图案选择性。例如,Bent等人108通过在每100个循环中注入蒸汽分子,开发了一种再生ALD工艺。该策略将选择性提高了三倍。为了改善弱选择性,有必要缩短官能化的时间间隔。Mackus等人112发现,在初始阶段,SiO2线性沉积在SiO2衬底上,而在TiO2、HfO2、CoOx和MoOx上的成核只有10〜15个周期的延迟。在每10个循环内添加乙酰丙酮作为抑制剂,可以明显提高选择性。此外,Elam等155在每个ALD循环前进行表面处理,以提高选择性,如图7(c)所示。通过重复校正的步骤(也称为ABC型循环),可以显著提高选择性。该方法克服了沉积过程中抑制剂的变性,并可以获得所需的高选择性。

另一种方法是将选择性刻蚀集成到选择性沉积过程中。选择性刻蚀,特别是原子层刻蚀(ALE),是去除非生长区域材料的有效方法。为了维持和改善生长区和非生长区之间的选择性,在ALD循环中添加选择性刻蚀,可以用于纳米结构制造。George等人156使用HF和金属前驱物作为反应物,并将基材暴露在HF气氛中以氟化一层原子,然后通过金属前驱物交换配体。最终,薄膜被逐层刻蚀。应当指出,金属氧化物仅与特定的金属前体反应。例如,Al(CH3)3仅与Al2O3的氟化基体反应,而不是SiO2、ZrO2、Si3N4和TiN(见图7(d))。Parsons比较了ALD循环和ALD + ALE超级循环157,超级循环的选择性是传统循环的10倍。采用超循环后,非生长Si区域的TiO2厚度从8.0 nm减小到零。此外,Mackus等人158在每100个循环中增加选择性刻蚀,以实现钌在Pt而非SiO2上的区域选择性沉积。800个循环后,在Pt区域沉积了8 nm的Ru,而SiO2区域却非常干净。ALE由于其各向同性和选择性而备受关注,它特别适用于传统的各向异性刻蚀无法实现的复杂三维结构。耦合原子尺度沉积和自上而下的刻蚀将成为研究重点,并且工业应用似乎即将到来。

图7.(a)紧密排列的ODTS薄膜和松散排列的ODTS薄膜之间的比较147;(b)SAMs的针孔作为ALD的成核位点150;(c)ABC型工艺155;(d)选择性刻蚀156。(a)经147许可转载。版权所有(2004)美国物理联合会:AIP出版社。(b)经150许可转载。版权所有(2015)施普林格-自然集团。(c)经155许可转载。版权所有(2013)美国化学会。(d)经156许可转载。版权所有(2016)美国化学会。

4.无模板的选择性沉积

在上一部分中,我们介绍了在各种模板的帮助下用于对齐的选择性沉积。然而,上述方法对于低维材料和复杂的三维结构具有局限性,因为寻找合适的模板是有挑战性的。许多工作已经研究了非模板的选择性沉积方法。由于没有模板限制并且出现了低维材料,因此本节研究的膜厚通常小于10 nm,在某些情况下,该部分的膜厚甚至只有一个原子级。非模板选择性沉积引起了人们的极大兴趣,因为它实际上不含任何抗蚀剂,抑制剂,蚀刻剂或剥离产物。为了实现高选择性,期望抑制非生长区域上的成核。近来,研究者利用非模板选择性沉积方法在特定材料上沉积了超薄膜,同时可以保持非生长区域清洁而无需其他处理。为了量化选择性,普遍接受的方程式如下130:

其中θGA和θNGA分别是原子核数或沉积在生长区和非生长区上的物质数量。在某些情况下,θ值会简化为膜厚。如果S = 1,则存在完美的选择性生长,并且在非生长表面上没有目标产物出现。如果S = 0,则根本没有选择性。关于选择性沉积,值得考虑的是实际应用中需要多高的选择性。

在本节中,将讨论固有的选择性、超尺度选择性沉积和单位点沉积。到目前为止,研究人员发现在金属(或准金属)与电介质之间出现了一些特定的选择性沉积反应,因为两种类型的基材呈现出不同的表面化学状态。这种类型的选择性沉积被分类为固有的选择性沉积,然后还讨论了直接写入沉积和相选择性沉积。对于超尺度选择性沉积,低维材料是讨论的重点,包括2D材料、纳米线、纳米粒子等。例如,通过选择性沉积可以消除2D材料中的线缺陷。另一种选择性沉积发生在纳米线或纳米粒子的不同晶面中,这称为晶面选择性沉积或位点选择性沉积。最后,选择性沉积扩展到单个位点,包括原子空位和单个原子。表2显示了许多非模板选择性沉积策略。在后硅时代,原子级沉积可以制备许多替代硅的纳米材料,例如2D材料、碳材料、铁电材料、相变材料等,这些材料可以克服硅材料的物理局限性并拓宽摩尔定律的边界。

表2. 非模板选择性沉积

4.1固有的选择性沉积

固有的选择性沉积利用了薄膜在不同材料上的成核延迟,而无需模板辅助。通常,一旦形核出现在非生长区域,选择性就很容易丧失。因此,它适用于超精细结构。在本节中,介绍了各种用于固有选择性沉积的图案化基板,例如Si / SiO2、金属/氧化物、氧化物/氧化物等。

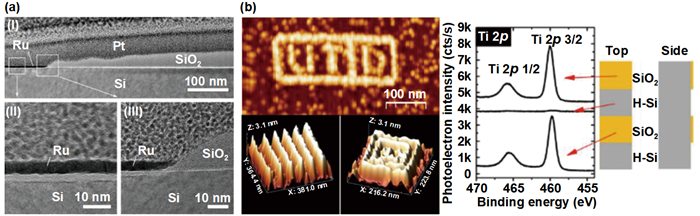

晶体管的发展推动了半导体和金属在Si / SiO2衬底上的固有选择性沉积。早在1962年,Joyce等人37报道了Si选择性沉积在Si衬底而不在SiO2上沉积。原因是在高温氢气氛围中存在成核与还原之间的竞争,因此使氧化物层上的成核速率最小化。类似地,Dendooven等人159发现了Ru沉积在SiO2上的成核延迟,并且通过原位光谱椭圆偏振法发现60个循环是在SiO2上生长的阈值(见图8(a))。值得注意的是,SiO2表面的羟基为HfO2和ZnO沉积提供了更多的活性反应位点,这与前面的工作有所不同。Roozeboom及其同事164,182通过EBID在Si衬底上得到了SiO2籽晶层,通过将温度从100℃升高到250℃,ALD上成核延迟从80循环升高到120循环。同样,Wallace等人183使用浸笔式纳米光刻技术获得了SiO2 / Si纳米图案,并且TiO2的形核仅发生在SiO2区域(见图8(b))。原因是ALD成核反应的前体(或共反应物)与表面基团之间的催化作用。固有的选择性通常仅在特定的材料体系中存在。对于实际应用,选择性窗口需要进一步调控。在不进行额外处理的情况下,开发更多材料并获得高选择性至关重要。

图8. 固有的选择性沉积:(a)Ru先在Si上而不在SiO2上沉积159,(b)TiO2先在SiO2上而不在Si上沉积183。(左)经159许可转载。版权所有(2019)美国化学会。(右)经183许可转载。版权所有(2013)美国化学会。

迄今为止,基于表面差异的固有选择性沉积已将其应用扩展到许多其他领域。在这一部分中,对金属/氧化物衬底的研究最多。核-壳催化剂促进了在贵金属而不是氧化物基底上的选择性沉积。Lu和他的同事184成功地沉积了双金属核-壳纳米粒子,同时避免了其在氧化物载体表面的生长。对于Pd和Pt的沉积,表面上的活性位分别为H *和O *。原子尺度沉积显示出在原子水平上优异的厚度控制和催化性能的改善。Kessels等人185发现,只有当Pd核大于1 nm时才会发生Pt壳的生长,而选择性主要来自金属和氧化物基质之间的不同表面能。他们163,186通过EBID制备种子层,随后通过选择性ALD得到了Pt纳米图案。Pt纳米线的横向分辨率仅为〜10 nm。EBID可以将基板预先构图成任何平面形状,因此一些研究人员将这些工艺称为直写ALD 182,187,188。由于没有刻蚀剂残留,因此直写ALD金属的接触电阻较低。这种方法是光刻的替代方法,并且与敏感的纳米材料更兼容。

除金属对金属外,还研究了氧化物对金属的选择性。Bent及其同事161发现,通过俄歇电子能谱的元素计数,Fe2O3-ALD对Pt和SiO2的选择性高达2000:1。另外,在带有铱图案的SiO2衬底上,Fe2O3和NiO-ALD的选择性分别为900:1和200:1。这种选择性不仅存在于图案化的双层膜中,而且存在于核/壳纳米颗粒中。氧化物基质不能催化共反应物O2,故不存在可参与ALD前体分解的活化O*。选择性来源于金属区域较低的化学吸附能和活化能。值得注意的是,无论是三维结构、二维平面还是纳米颗粒,金属和氧化物表面活性的差异总是存在的。由于上述原因,一旦合适的前体材料出现,两种不同材料之间的固有选择性总是存在的。

与上述区域选择性沉积不同,相选择性沉积方法允许不同的相在异种表面同步生长189。Horwat等人165利用电子束光刻技术制备了ZnO/Al-ZnO图案化薄膜。经过10000次ALD循环后,Cu选择性地沉积在Al掺杂的ZnO区域,Cu2O选择性地生长在ZnO区域。作者将其归因于基质的导电性。Cu生长在高导电区,Cu2O沉积在低导电区。这种选择性很难存在,因此很少有报道。相信这种沉积将极大地拓展选择性沉积的应用。

4.2超尺度选择性沉积

现在,半导体行业进入了超尺度时代,低维材料的应用方兴未艾,例如2D材料、1D纳米线、纳米粒子等。由于相同材料上的表面物种相同,因此非常难以实现选择性沉积。在这种情况下,自由能的微小差异是实现选择性的可能途径。在这一部分中,将讨论超尺度选择性沉积及其在电子、催化、显示、储能等领域的研究进展。

为扩展并超越摩尔定律,2D材料是FET沟道材料的有前途的候选者190-193。Liu等人194通过ALD合成了仅具有几个原子单层的2D MoS2。由于中间层的弱范德华力很容易被破坏,层数可以控制为1到10。类似地,半导体材料也可以进行处理以获得分层结构。Buhro等人195合成了具有均匀单层厚度的2D半导体纳米晶体。尽管2D材料的厚度仅为纳米级或亚纳米级,但与块状Si材料相比,它们没有短沟道效应。同样,出色的移动性使其成为后硅电子产品的有希望的候选者。2D材料只能沉积在某些特定的基材上,因此如何选择性地将它们沉积成特定的形状并将它们集成到半导体生产线中是困难的。

对于2D材料的制造,研究者探索了许多方法。二维石墨烯中的一维缺陷会使其电学性能变差,目前已经开发出在缺陷上选择性沉积金属的方法166-168,196,197。Bao及其同事166发现,在500次ALD循环后,Pt选择性沉积在CVD石墨烯的线缺陷上。1000次循环后,孤立的Pt在点缺陷处出现。在300个循环中,作者计算出晶界处的Pt成核密度比晶粒表面高440倍。研究人员将其归功于不同的反应能。此外,电子束沉积(EBID)和电子束雕刻(EBIS)已成为制造2D材料埃级分辨率结构的重要方法198。这些方法不仅有利于电子学的发展,而且还应用于新兴的传感、催化、能源等领域。

选择性沉积发生在两种类型的材料是基于不同的活性位点。但是对于均质的低维材料,唯一的区别来自具有不同表面活性的不同晶面。近年来,人们对基于低维结构的气相选择性方法进行了许多尝试,以扩展摩尔定律。Lieber等人169通过CVD合成了Si纳米线。然后在Si模板上生长三种类型的Ge壳。通过在380℃下注入GeH4,Ge无差别的沉积沉积在纳米线的表面,生长速度约为10 nm / min。在相同温度下添加PH3和Ar后,生长速率按(111)、(011)和(113)的顺序增加。在330℃通入H2的过程中,实现了很高的选择性,Ge仅在(111)(2 nm / min)和(011)(1 nm / min)表面而不在(113)表面上生长。此外,他们发现,只有在650℃使用Si前驱体和H2的情况下,Si才在Si纳米线的(111)表面上选择性生长。在沉积过程中控制工艺窗口至关重要,包括温度、压力、气体类型和流速等。这种选择性调节方法在纳米线晶体管中具有广阔的前景。

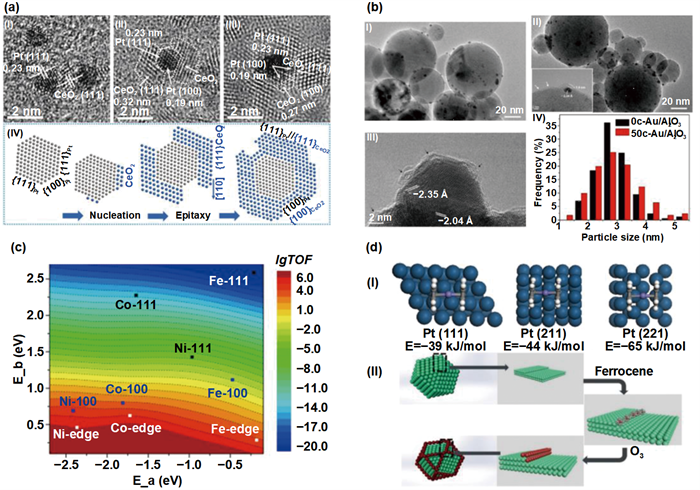

对于零维结构,许多研究人员发现在Au 175、TiO2 199、200、Ag 201和量子点173纳米粒子上可以通过液相沉积获得选择性包覆结构。基于纳米颗粒的选择性主要受催化领域的驱动。我们176通过晶面选择性ALD制备了纳米栅栏CeOx / Pt结构催化剂。CeOx选择性沉积在Pt(111)刻面上以防止烧结,而具有较高催化活性的Pt(100)刻面则暴露出来(见图9(a))。此外,Lu等人202发现,TiO2首先覆盖了Au的低配位位点(见图9(b))。在5个ALD循环之前,由于Au-TiO2界面的形成,催化活性显著提高。经过20个ALD循环后,活性位点逐渐被覆盖。催化性能受沉积氧化物厚度的影响很大。迄今为止,我们已经报道了催化领域的几种选择性ALD方法,包括嵌入结构、不连续涂层结构和核-壳结构等203。

我们还研究了棱边选择性ALD(见图9(c)),M(Cp)2(M = Fe,Co和Ni)前体在Pt纳米颗粒上沉积的优先顺序为边缘>(100)>(111),这已通过第一性原理计算得到验证204,205。此外,Qin等人206发现FeOx首先修饰了(221),其次是(211)和(111),与吸附能以(221)>(211)>(111)的顺序降低相吻合(见图9(d))。低维结构选择性可以通过热力学和动力学对其进行进一步优化,以获得高选择性,例如前体活性、腔体压力、反应温度等。

图9. 纳米粒子的选择性沉积:(a)纳米栅栏的CeOx / Pt结构176;(b)TiO2包覆Au的低配位位点202;(c)通过第一性原理计算验证了棱边选择性ALD 205;(d)吸附能的计算206。(a)经176许可转载。版权所有(2017)威利- VCH出版社。(b)经202许可转载。版权所有(2015)美国化学会。(c)经205许可转载。版权所有(2018)美国化学会。(d)经206许可转载。版权所有(2017)爱思唯尔集团。

4.3单位点沉积

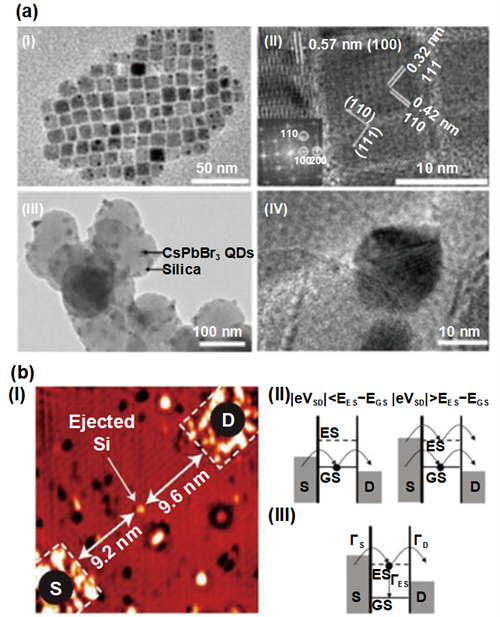

由于显示和能源的应用,位点选择性沉积进入了人们的视线。例如,钙钛矿量子点可以通过ALD涂覆纳米级氧化铝来稳定(见图10(a))207。在ALD过程中,没有长链保护的区域不存在氧化铝,而未保护的位点被选择性地钝化。100分钟后性能没有明显下降,而未经处理的性能在1分钟内降至零。对于P型半导体,空位缺陷会降低材料的性能208。Cahoon等181通过ALD选择性地钝化了空位缺陷。由于空位上存在高活性的氧键,只能在空位上发生定点沉积,使得太阳能电池的性能提高了3倍。以上性能提高是许多孤立的单位点选择性沉积的协同效应。

除纳米颗粒外,单原子还显示了其在半导体纳米器件上的潜在应用。单原子晶体管被认为是超尺度时代有前途的解决方案179。Simmons等人180,209通过化学掺杂以原子精度将单个P原子掺杂到了外延Si表面中(参见图10(b))。饱和剂量诱导三个PH3分子在三个二聚体位点解离。加热到350℃后,PH2经历了两个解离成单个P原子。最后,伴随着硅原子的喷射,Pt原子掺入了Si晶格的表面。除化学方法外,还有多种对单个原子进行物理处理的方法,包括AFM 210、STM 211和STEM 212。未来,商业化单原子操纵技术的发展将成为原子或近原子尺度制造的制高点。

图10.(a)量子点207;(b)单原子晶体管209。(上)经207许可转载。版权所有(2018)美国化学会。(下)经209许可转载。版权所有(2017)美国化学会。

5.总结与展望

在这篇综述中,我们总结了用于纳米材料和纳米结构的原子尺度沉积方法的发展,这将扩展甚至超越摩尔定律。为了提高晶体管的密度,开发了双重图案化和多重图案化方法。这些过程的特征是使水平亚纳米分辨率转移到垂直方向。类似的方法还可以用来制造多种纳米结构,例如纳米线、纳米孔、纳米管等。另一方面,高精度对准已成为制造复杂三维结构的主要挑战。选择性沉积可以实现与基底图案的自对准,并简化制造过程。为了实现对准的堆叠结构,开发了两种类型的选择性沉积方法,包括模板辅助选择性沉积和固有的选择性沉积。为了进一步减小器件的尺寸,还研究了原子级沉积方法来制造超尺度的纳米结构,例如纳米片、纳米线、纳米颗粒和单原子。

为了实现高精度的纳米制造,原子尺度沉积的机理需要深入研究。首先,在沉积初期的生长行为至关重要,因为它决定了薄膜的形核和质量。例如,可以通过促进层状生长并抑制岛状成核来降低表面粗糙度。然后,为了获得高质量的薄膜,有必要探索工艺窗口以减少缺陷的形成和副产物的污染。最后,需要开发用于制造全过程监测的原位表征方法。反应机理的原位研究可提供进一步改进沉积方法所需的更多信息。

尽管表征技术正在蓬勃发展,但单原子表征和操纵技术仍有很大的改进空间。未来,微纳制造将以超高精度的趋势发展,特别是在半导体工业中。在原子和接近原子的尺度上,需要诸如AFM、STM和STEM之类的方法来实现直接的操纵和表征。AFM具有适应性强的优势,无需表面处理和真空环境。而且,它对几乎所有类型的材料都具有很强的扩展性。但是,非实时测量是AFM的最大障碍。对于STM,它仅适用于导电材料,并且对材料的表面和机械振动敏感。到目前为止,它可以非常灵活地用于极低温检测、超快速扫描、液相测试等。至于STEM,它只能测试没有3D形貌的超薄纳米材料,但分辨率可以低至0.05 nm。尽管上述技术是原子物理和化学的强大工具,但对于快速稳定的原子操纵来说,它们仍处于起步阶段。

为了实现复杂的纳米结构制造,多种工艺的耦合是必不可少的。常规工艺已广泛应用于图案化、光刻、刻蚀和剥离工艺。然而,在半导体工业中仅采用了几种选择性沉积方案,这主要是因为只有很少的材料获得了高选择性。通过优化沉积工艺来获得新材料的选择性沉积具有重要意义。为了平衡沉积速率和台阶覆盖率,使用组合的沉积方法(例如PVD、CVD、ALD等)非常有效。新开发的空间隔离ALD有望用于提高大面积生产的效率213。由于要在精度和效率之间进行权衡,因此原子级沉积和自上而下刻蚀相结合的方法对于具有指数复杂性的多维结构制造可能具有吸引力。因此,在选择性沉积之后,需要诸如原子层刻蚀和拓扑刻蚀之类的减材过程,以去除非生长区域上的杂质。

另外,原子级沉积方法的集成对于芯片制造过程中的跨尺度处理也具有很大的优势。广泛的应用需求将促进从原子操作、原子/分子自组装、纳米粒子合成到多维结构的跨尺度加工,这将增加工艺的复杂性和耦合难度。在跨尺度制造中,需要考虑如下问题,例如界面效应、对准和热管理。3D集成和封装是有前途的架构,可克服尺寸限制并提高设备性能,例如芯片对芯片、芯片对晶片、晶片对晶片策略。边缘平整度和平滑的界面控制将是3D集成中原子级沉积的重要考虑因素,需要精确控制压力、温度、流速等。此外,需要许多创新方案来应对缺陷容忍度和热密度的挑战。这些方法提供了异构集成和单片3D集成,将有助于实现高密度和多功能,用以扩展摩尔定律。此外,多维制造技术对于“more Moore”和“more than Moore”应用都有巨大的潜力214。

对于高精度制造,精度和加工效率是相互抑制的因素。期望开发用于实现高通量生产的制造设备。另一方面,设备的复杂性要求后端设备支持异构集成和组装。为了满足高价值异构系统集成的需求,有必要加快集成前端设备和后端设备。

开发原子级沉积可以扩展摩尔定律并扩展到更多用途。对于微电子学而言,沉积将继续发挥重要作用,其关键尺寸可降至7纳米以下。令人欣喜的是,优化的沉积方法可以改善纳米器件的性能和稳定性。原子尺度沉积方法在能源、环境、生物医学、柔性电子等新兴应用也具有潜力。因此,摩尔定律的应用不仅限于微电子制造,它将成为支持光学、磁性、声学和生物技术等领域的平台,以实现超越硅基电子技术的转变。在这些方面,原子尺度沉积仍然起着超越摩尔定律的重要作用。

总之,原子级沉积为微纳制造的发展,特别是在半导体工业中的发展提供了技术驱动力。首先,加工精度范围从微米到纳米甚至原子级。其次,沉积材料从传统的半导体和金属扩展到新兴的2D材料、碳材料、铁电材料等。另外,所制造的结构包括高纵横比结构、纳米管、纳米线、纳米颗粒等。最后,3D集成允许高密度放置和功能多样化的实现。因此,原子尺度沉积可以高精度地集成纳米材料、纳米结构、纳米器件和纳米系统,从而扩展并超越摩尔定律。

6.致谢

本工作得到了国家自然科学基金(51835005、51702106、51871103、51575217)和华中科技大学国家重点实验室项目(DMETKF2019003)的资助。作者感谢单斌教授、文艳伟教授的建设性意见。作者还要感谢华中科技大学分析测试中心和柔性电子研究中心的支持。

下载:

下载: