10nm及以下技术节点晶圆缺陷光学检测

-

摘要:

综述 ● 开放获取阅读更多

1. 文章导读

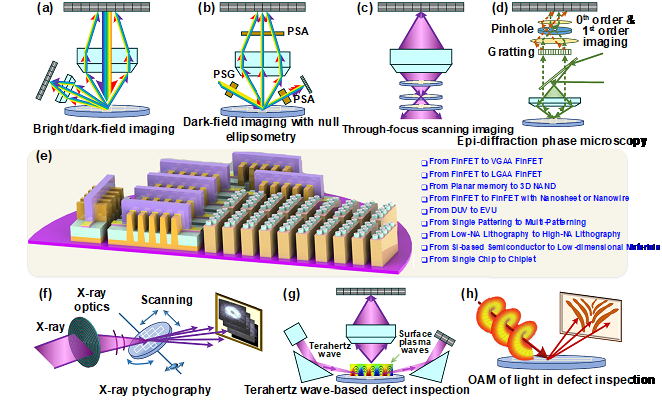

伴随智能终端、无线通信与网络基础设施、智能驾驶、云计算、智慧医疗等产业的蓬勃发展,先进集成电路的关键尺寸进一步微缩至亚10nm尺度,图形化晶圆上制造缺陷(包括随机缺陷与系统缺陷)的识别、定位和分类变得越来越具有挑战性。传统明场检测方法虽然是当前晶圆缺陷检测的主流技术,但该方法受制于光学成像分辨率极限和弱散射信号捕获能力极限而变得难以为继,因此亟需探索具有更高成像分辨率和更强缺陷散射信号捕获性能的缺陷检测新方法。近年来,越来越多的研究工作尝试将传统光学缺陷检测技术与纳米光子学、光学涡旋、计算成像、定量相位成像和深度学习等新兴技术相结合,以实现更高的缺陷检测灵敏度,这已为该领域提供了新的可能性。近期,华中科技大学机械科学与工程学院、数字制造装备与技术国家重点实验室的刘世元教授、朱金龙研究员、刘佳敏博士后、江浩教授、谷洪刚讲师,哈尔滨工业大学张泽旭教授、徐田来副教授、袁帅副教授,和香港中文大学周仁杰助理教授在SCIE期刊《极端制造》(International Journal of Extreme Manufacturing, IJEM)上共同发表了《10nm及以下技术节点晶圆缺陷光学检测》的综述,对过去十年中与光学晶圆缺陷检测技术有关的新兴研究内容进行了全面回顾,并重点评述了三个关键方面:(1)缺陷可检测性评估,(2)多样化的光学检测系统,以及(3)后处理算法。图1展示了该综述研究所总结的代表性晶圆缺陷检测新方法,包括明/暗场成像、暗场成像与椭偏协同检测、离焦扫描成像、外延衍射相位显微成像、X射线叠层衍射成像、太赫兹波成像缺陷检测、轨道角动量光学显微成像。通过对上述研究工作进行透彻评述,从而阐明晶圆缺陷检测技术的可能发展趋势,并为该领域的新进入者和寻求在跨学科研究中使用该技术的研究者提供有益参考。

亮点:

● 透彻梳理了有望实现10nm及以下节点晶圆缺陷检测的各类光学新方法。

● 建立了晶圆缺陷可检测性的评价方法,总结了缺陷可检测性的影响因素。

● 简要评述了传统后处理算法、基于深度学习的后处理算法及其对缺陷检测性能的积极影响。

图1 能够应对图形化晶圆缺陷检测挑战的各类光学检测系统示意图。(a)明/暗场成像;(b)暗场成像与椭偏协同检测;(c)离焦扫描成像;(d)外延衍射相位显微成像;(e)包含逻辑芯片与存储芯片的图形化晶圆;(f)X射线叠层衍射成像;(g)太赫兹成像;(h)轨道角动量光学显微成像。

2. 研究背景

伴随智能手机、平板电脑、数字电视、无线通信基础设施、网络硬件、计算机、电子医疗设备、物联网、智慧城市等行业的蓬勃发展,不断刺激全球对半导体芯片的需求。这些迫切需求,以及对降低每片晶圆成本与能耗的不懈追求,构成了持续微缩集成电路关键尺寸和增加集成电路复杂性的驱动力。目前,IC制造工艺技术已突破5nm,正朝向3nm节点发展,这将对工艺监控尤其是晶圆缺陷检测造成更严峻的考验:上述晶圆图案特征尺寸的微缩,将极大地限制当前晶圆缺陷检测方案在平衡灵敏度、适应性、效率、捕获率等方面的能力。随着双重图案化、三重图案化以及四重图案化紫外光刻技术的广泛使用,检测步骤的数量随着图案化步骤的增加而显著增加,这可能会降低产率并增加器件故障的风险,因为缺陷漏检事故的影响会被传递至最终的芯片制造流程中。更糟糕的是,当前业界采用极其复杂的鳍式场效应晶体管 (FinFET) 和环栅 (GAA) 纳米线 (NW) 器件来降低漏电流和提高器件的稳定性,这将使得三维 (3D) 架构中的关键缺陷通常是亚表面(尤其是空隙)缺陷、深埋缺陷或高纵横比结构中的残留物。总体上而言,伴随工业界开始大规模的10 纳米及以下节点工艺芯片规模化制造,制造缺陷对芯片产量和成本的影响变得越来越显著,晶圆缺陷检测所带来的挑战无疑会制约半导体制造产业的发展。鉴于此,IC芯片制造厂商对晶圆缺陷检测技术与设备的重视程度日渐加深。在本文中,朱金龙研究员等人对图形化晶圆缺陷光学检测方法的最新进展进行了详细介绍。

3. 最新进展

晶圆缺陷光学检测方法面的最新进展包含三个方面:缺陷可检测性评估、光学缺陷检测方法、后处理算法。

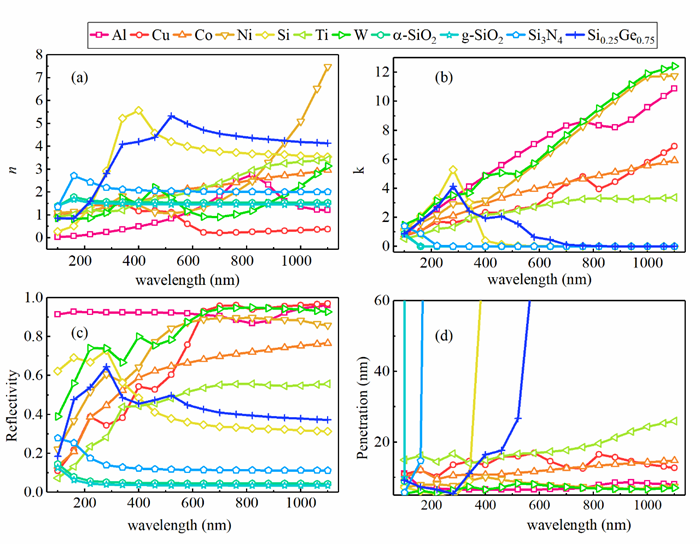

缺陷可检测性评估包含两个方面:材料对缺陷可检测性的影响、晶圆缺陷拓扑形貌对缺陷可检测性的影响。图2展示了集成电路器件与芯片中所广泛采纳的典型体材料的复折射率N、法向反射率R和趋肤深度δ。针对被尺寸远小于光波长的背景图案所包围的晶圆缺陷,缺陷与背景图案在图像对比度差异主要是由材料光学特性的差异所主导的,也就是复折射率与法向反射率。具体而言,图2(c)所示的缺陷材料与图案材料的法向反射率曲线差异是优化缺陷检测光束光谱的基础之一。因此,寻找图像对比度和灵敏度足够高的最佳光束光谱范围比纯粹提高光学分辨率更重要一些,并且此规律在先进工艺节点下的晶圆缺陷检测应用中更具指导意义。

图2 集成电路中典型体材料的光学特性。(a)折射率n;(b)消光系数k;(c)法向反射率R;(d)趋肤深度δ。

晶圆缺陷拓扑形貌对缺陷可检测性的影响也尤为重要。在图形化晶圆缺陷检测中,缺陷散射信号信噪比和图像对比度主要是受缺陷尺寸与缺陷类型影响的。图3展示了存储器件中常规周期线/空间纳米结构中的典型缺陷,依次为断线、边缘水平桥接和通孔、凹陷、之字形桥接、中心水平桥接、颗粒、突起、竖直桥接等缺陷。目前,拓扑形貌对缺陷可检测性的影响已被广泛研究,这通常与缺陷检测条件配置优化高度相关。例如,水平桥接与竖直桥接均对照明光束的偏振态相当敏感;在相同的缺陷检测条件配置下,桥接、断线、颗粒物等不同类型的缺陷会展现出不同的缺陷可检测性;同时,缺陷与背景图案的尺寸亦直接影响缺陷的可检测性,尺寸越小的缺陷越难以被检测。

图3 图形化晶圆上周期线/空间纳米结构中的典型缺陷(a)断线;(b)边缘水平桥接和通孔;(c)凹陷;(d)之字形桥接缺陷;(e)中心水平桥接;(f)颗粒物;(g)突起;(h)竖直桥接。

丰富多彩的新兴光学检测方法。光是人眼或人造探测器所能感知的电磁波谱范围内的电磁辐射。任意光电场可采用四个基本物理量进行完整描述,即频率、振幅、相位和偏振态。晶圆缺陷光学检测通常是在线性光学系统中实施的,从而仅有频率不会伴随光与物质相互作用发生改变,振幅、相位、偏振态均会发生改变。那么,晶圆缺陷光学检测系统可根据实际使用的光学检测量进行分类,具体可划分为明/暗场成像、暗场成像与椭偏协同检测、离焦扫描成像、外延衍射相位显微成像、X射线叠层衍射成像、太赫兹波成像缺陷检测、轨道角动量光学显微成像。图4展示了基于相位重构的光学缺陷检测系统,具体包括外延相位衍射显微成像系统、光学伪电动力学显微成像系统。在这两种显微镜成像系统中,缺陷引起的扰动波前信号展现了良好的信噪比,并且能够被精准地捕获。

后处理算法。从最简单的图像差分算子到复杂的图像合成算法,后处理算法因其能显著改善缺陷散射信号的信噪比和缺陷-背景图案图像对比度而在光学缺陷检测系统中发挥关键作用。伴随着深度学习算法成为普遍使用的常规策略,后处理算法在缺陷检测图像分析场景中的价值更加明显。典型后处理算法如Die-to-Die检测方法是通过将无缺陷芯片的图像与有缺陷芯片的图像进行比较以识别逻辑芯片中的缺陷,其也被称为随机检测。Cell-to-Cell检测方法是通过比较将同一芯片中无缺陷单元的图像与有缺陷单元的图像进行比较以识别存储芯片中的缺陷,其也被称为阵列检测。至于Die-to-Database检测方法,其本质是通过将芯片的图像与基于芯片设计布局的模型图像进行比较以识别芯片的系统缺陷。而根据原始检测图像来识别和定位各类缺陷,关键在于确保后处理图像(例如差分图像)中含缺陷区域的信号强度应明显大于预定义的阈值。基于深度学习的缺陷检测方法的实施流程非常简单:首先,捕获足够的电子束检测图像或晶圆光学检测图像(模拟图像或实验图像均可);其次,训练特定的神经网络模型,从而实现从检测图像中提取有用特征信息的功能;最后,用小样本集测试训练后的神经网络模型,并根据表征神经网络置信水平的预定义成本函数决定是否应该重复训练。然而,深度学习算法在实际IC生产线中没有被广泛地接收,尤其是在光学缺陷检测方面。其原因不仅包括“黑箱性质”和缺乏可解释性,还包括未经实证的根据纯光学图像来定位和分类深亚波长缺陷的能力。而要在IC制造产线上光学缺陷检测场景中推广深度学习技术的应用,还需开展更多研究工作,尤其是深度学习在光学缺陷检测场景中的灰色区域研究、深度学习与光学物理之间边界的探索等。

图4 代表性新兴晶圆缺陷光学检测系统。(a)外延相位衍射显微成像系统;(b)光学伪电动力学显微成像系统。(a)经许可转载。版权所有(2013)美国化学会。(b)经许可转载。版权所有(2019)美国化学会。

4. 未来展望

伴随集成电路(IC)制造工艺继续向10nm及以下节点延拓,针对IC制造过程中的关键工序开展晶圆缺陷检测,从而实现IC制造的工艺质量监控与良率管理,这已成为半导体领域普遍达成的共识。尽管图形化晶圆缺陷光学检测一直是一个长期伴随IC制造发展的工程问题,但通过与纳米光子学、结构光照明、计算成像、定量相位成像和深度学习等新兴技术的融合,其再次焕发活力。其前景主要包含以下方面:为了提高缺陷检测灵敏度,需要从检测系统硬件与软件方面协同创新;为了拓展缺陷检测适应性,需要更严谨地研究缺陷与探测光束散射机理;为了改善缺陷检测效率,需要更高效地求解缺陷散射成像问题。除了IC制造之外,上述光学检测方法对光子传感、生物感知、混沌光子等领域都有广阔的应用前景。

下载:

下载: